### 1.1 Introduction of STC15W201S series MCU (In abundant supply)

STC15W201S series MCU is a single-chip microcontroller based on a high performance 1T architecture 8051 CPU, which is produced by STC MCU Limited. It is a new generation of 8051 MCU of high speed, high stability, wide voltage range, low power consumption and super strong anti-disturbance. Besides, STC15W201S series MCU is a MCU of super advanced encryption, because it adopts the ninth generation of STC encryption technology. With the enhanced kernel, STC15W201S series MCU is faster than a traditional 8051 in executing instructions (about 8~12 times the rate of a traditional 8051 MCU), and has a fully compatible instruction set with traditional 8051 series microcontroller. External expensive crystal can be removed by being integrated internal high-precise R/C clock( $\pm 0.3\%$ ) with  $\pm 1\%$  temperature drift ( $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ ) while  $\pm 0.6\%$  in normal temperature ( $-20^{\circ}\text{C} \sim +65^{\circ}\text{C}$ ) and wide frenquency adjustable between 5MHz and 35MHz. External reset curcuit also can be removed by being integrated internal highly reliable one with 16 levels optional threshold voltage of reset. The STC15W201S series MCU includes a high-speed asynchronous serial port----UART( can be regarded as 2 serial ports by shifting among 2 groups of pins), comparator and so on. STC15W201S series MCU is usually used in serial communication or electrical control or some occasion with strong disturbance.

In Keil C development environment, select the Intel 8052 to compiling and only contain < reg51.h > as header file.

STC15 series MCU with super high-speed CPU core of STC-Y5 works 20% faster than STC early 1T series (such as STC12/STC11/STC10 series) at same clock frequency.

- Enhanced 8051 Central Processing Unit, 1T, single clock per machine cycle, faster 8~12 times than the rate of a traditional 8051.

- Operating voltage range: 5.5V ~ 2.4V.

- On-chip 1K/2K/3K/4K/5K/7.5K FLASH program memory with flexible ISP/IAP capability, can be repeatedly

erased more than 100 thousand times.

- · on-chip 256 bytes SRAM

- On-chip EEPROM with large capacity can be repeatedly erased more than 100 thousand times.

- ISP/IAP, In-System-Programming and In-Application-Programming, no need for programmer and emulator.

- Internal hghly reliable Reset with 16 levels optional threshold voltage of reset, external reset curcuit can be completely removed

- Internal high- precise R/C clock(±0.3%) with ±1% temperature drift (-40°C~+85°C) while ±0.6% (-20°C ~+65°C) in normal temperature and wide frenquency adjustable between 5MHz and 35MHz (5.5296MHz / 11.0592MHz / 22.1184MHz / 33.1776MHz).

- Operating frequency range: 0-35MHz, is equivalent to traditional 8051:0~420MHz.

- No need external crystal and reset, and can output clock and low reset signal from MCU.

- A high-speed asynchronous serial ports----UART ( can be regarded as 2 serial ports by shifting among 2 groups of pins): UART1(RxD/P3.0, TxD/P3.1) can be switched to (RxD\_2/P3.6, TxD\_2/P3.7).

- Support the function of Encryption Download (to protect your code from being intercepted).

- Support the function of RS485 Control

- Code protection for flash memory access, excellent noise immunity, very low power consumption

- Power management mode: Slow-Down mode, Idle mode(all interrupt can wake up Idle mode), Stop/Power-Down mode.

- Timers which can wake up stop/power-down mode: have internal low-power special wake-up Timer.

- Resource which can wake up stop/power-down mode are: INT0/P3.2, INT1/P3.3 (INT0/INT1, may be

generated on both rising and falling edges), INT2/P3.6, INT3/P3.7, INT4/P3.0 (INT2/INT3/INT4, only be generated on falling edge); pins T0/T2(their falling edge can wake up if T0/T2 have been enabled before power-down mode, but no interrupts can be generatetd); internal low-power special wake-up Timer.

- Two Timers/Counters----T0(are compatible with Timer0 of traditional 8051) and T2, T0/T2 all can independently achieve external programmable clock output

- Programmable clock output function(output by dividing the frequency of the internal system clock or the input clock of external pin):

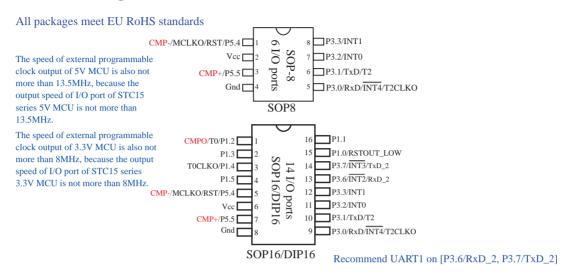

- The speed of external programmable clock output of 5V MCU is also not more than 13.5MHz, because the output speed of I/O port of STC15 series 5V MCU is not more than 13.5MHz.

- The speed of external programmable clock output of 3.3V MCU is also not more than 8MHz, because the output speed of I/O port of STC15 series 3.3V MCU is not more than 8MHz.

- ① The Programmable clock output of T0 is on P3.5/T0CLKO (output by dividing the frequency of the internal system clock or the input clock of external pin T0/P3.4)

- ② The Programmable clock output of T2 is on P3.0/T2CLKO (output by dividing the frequency of the internal system clock or the input clock of external pin T2/P3.1)

Two timers/counters in above all can be output by dividing the frequency from 1 to 65536.

③ The Programmable clock output of master clock is on P5.4/MCLKO, and its frequency can be divided into MCLK/1, MCLK/2, MCLK/4.

The master clock can either be internal R/C clock or the external input clock or the external crystal oscillator.

MCLK is the frequency of master clock. MCLKO is the output of master clock.

It is on MCLKO/P3.4 that the Programmable clock output of master clock of STC15 series 8-pin MCU (such as STC15F101W series). However, it is on MCLKO/P5.4 that the Programmable clock output of master clock of other STC15 series MCU including 16-pin or more than 16-pin MCU(such as STC15F2K60S2, STC15W4K32S4 and so on)

- Comparator, which support comparing by external pin CMP+ and CMP- or internal reference voltage and generating output signal (its polarity can be configured) on CMPO pin can be used as 1 channel ADC or brownout detect function.

- One 15 bits Watch-Dog-Timer with 8-bit pre-scaler (one-time-enabled)

- advanced instruction set, which is fully compatible with traditional 8051 MCU, have hardware multiplication / division command.

- 14/6 common I/O ports are available, their mode is quasi\_bidirectional/weak pull-up (traditional 8051 I/O ports mode) after reset, and can be set to four modes: quasi\_bidirectional/weak pull-up, strong push-pull/

strong pull-up, input-only/high-impedance and open drain.

the driving ability of each I/O port can be up to 20mA, but the current of the whole chip don't exceed this maximum 90mA.

If I/O ports are not enough, it can be extended by connecting a 74HC595(reference price: RMB 0.15 yuan). Besides, cascading several chips also can extend to dozens of I/O ports.

- Package: SOP-8, DIP-8, SOP-16(6mm x 9mm), DIP-16.

- All products are baked 8 hours in high-temperature 175°C after be packaged, Manufacture guarantee good quality.

- In Keil C development environment, select the Intel 8052 to compiling and only contain < reg51.h > as header file.

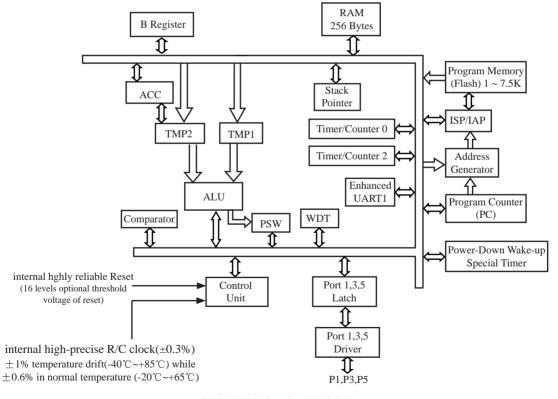

## 1.2 Block diagram of STC15W201S series

The internal structure of STC15W201S series MCU is shown in the block diagram below. STC15W201S series MCU includes central processor unit(CPU), program memory (Flash), data memory(SRAM), Timers/Counters, power-down wake-up Timer, I/O ports, high-speed asynchronous serial communication port---UART, Comparator, Watchdog, internal high- precise R/C clock, internal highly reliable Reset and so on.

STC15W201S series Block Diagram

### 1.3 Pin Configurations of STC15W201S series MCU

#### TOCLKO refers to the programmable clock output of Timer/Counter 0

(output by dividing the frequency of the internal system clock or the input clock of external pin T0/P3.4);

#### T2CLKO refers to the programmable clock output of Timer/Counter 2

(output by dividing the frequency of the internal system clock or the input clock of external pin T2/P3.1);

In addition to programmable output on the internal system clock, TOCLKO/T2CLKO also can be used as divider by dividing the frequency of the internal system clock or the input clock of external pin T0/T2.

MCLKO is the output of master clock whose frequency can be divided into MCLK/1, MCLK/2, MCLK/4

The master clock can either be internal R/C clock or the external input clock or the external crystal oscillator.

MCLK is the frequency of master clock.

| Mnemonic           | Add | Name                    | 7       | 6       | 5      | 4      | 3       | 2      | 1     | 0     | Reset<br>Value |

|--------------------|-----|-------------------------|---------|---------|--------|--------|---------|--------|-------|-------|----------------|

| AUXR1<br>P_SW1     | А2Н | Auxiliary register 1    | S1_S1   | S1_S0   | CCP_S1 | CCP_S0 | SPI_S1  | SPI_S0 | 0     | DPS   | 01xx,xx0x      |

| CLK_DIV<br>(PCON2) | 97H | Clock Division register | MCKO_S1 | MCKO_S0 | ADRJ   | Tx_Rx  | Tx2_Rx2 | CLKS2  | CLKS1 | CLKS0 | 00x0,x000      |

| UART1/S | UART1/S1 can be switched in 2 groups of pins by selecting the control bits S1_S0. |  |  |  |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| S1_S0   | UART1/S1 can be switched between P1 and P3                                        |  |  |  |  |  |  |  |  |

| 0       | UART1/S1 on [P3.0/RxD,P3.1/TxD]                                                   |  |  |  |  |  |  |  |  |

| 1       | UART1/S1 on [P3.6/RxD_2,P3.7/TxD_2]                                               |  |  |  |  |  |  |  |  |

Recommed UART1 on [P3.6/RxD\_2, P3.7/TxD\_2].

| Mnemonic           | Add | Name                    | 7       | 6       | 5    | 4     | 3       | 2     | 1     | 0     | Reset Value |

|--------------------|-----|-------------------------|---------|---------|------|-------|---------|-------|-------|-------|-------------|

| CLK_DIV<br>(PCON2) | 97H | Clock Division register | MCKO_S1 | MCKO_S0 | ADRJ | Tx_Rx | Tx2_Rx2 | CLKS2 | CLKS1 | CLKS0 | 00x0,x000   |

| MCKO_S1 | MCKO_S0 | the control bit of master clock output by dividing the frequency (The master clock can either be internal R/C clock or the external input clock or the external crystal oscillator) |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 0       | Master clock do not output external clock                                                                                                                                           |

| 0       | 1       | Master clock output external clock, but its frequency do not be divided, and the output clock frequency = MCLK / 1                                                                  |

| 1       | 0       | Master clock output external clock, but its frequency is divided by 2, and the output clock frequency = MCLK / 2                                                                    |

| 1       | 1       | Master clock output external clock, but its frequency is divided by 4, and the output clock frequency = MCLK / 4                                                                    |

The master clock can either be internal R/C clock or the external input clock or the external crystal oscillator. MCLK is the frequency of master clock.

STC15204SW series MCU output master clock on MCLKO/P5.4

It is on MCLKO/P3.4 that the Programmable clock output of master clock of STC15 series 8-pin MCU (such as STC15F101W series). However, it is on MCLKO/P5.4 that the Programmable clock output of master clock of other STC15 series MCU including 16-pin or more than 16-pin MCU.

#### Tx Rx: the set bit of relay and broadcast mode of UART1

0: UART1 works on normal mode

1: UART1 works on relay and broadcast mode, that to say output the input level state of RxD port to the outside TxD pin in real time, namely the external output of TxD pin can reflect the input level state of RxD port.

the RxD and TxD of UART1 can be switched in 3 groups of pins: [RxD/P3.0, TxD/P3.1];  $[RxD\_2/P3.6, TxD\_2/P3.7]; \\ [RxD\_3/P1.6, TxD\_3/P1.7].$

| CLKS2 | CLKS1 | CLKS0 | the control bit of system clock<br>(System clock refers to the master clock that has been divided frequency, which is offered to CPU and Timers) |

|-------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0     | 0     | Master clock frequency/1, No division                                                                                                            |

| 0     | 0     | 1     | Master clock frequency/2                                                                                                                         |

| 0     | 1     | 0     | Master clock frequency/4                                                                                                                         |

| 0     | 1     | 1     | Master clock frequency/8                                                                                                                         |

| 1     | 0     | 0     | Master clock frequency/16                                                                                                                        |

| 1     | 0     | 1     | Master clock frequency/32                                                                                                                        |

| 1     | 1     | 0     | Master clock frequency/64                                                                                                                        |

| 1     | 1     | 1     | Master clock frequency/128                                                                                                                       |

The master clock can either be internal R/C clock or the external input clock or the external crystal oscillator.

### 1.4 STC15W201S series Selection and Price Table

| Type<br>1T 8051<br>MCU                        | Operating<br>Voltage<br>(V) | Flash<br>(byte) | SRAM<br>(byte) | U<br>A<br>F<br>R |   | PCA | down   | Standard<br>External<br>Interrupts | & channal | C<br>M<br>P<br>A<br>R<br>A<br>T<br>O<br>R | P<br>T | EEP<br>ROM | X7-14      | Т   | Internal<br>High-<br>reliable<br>Reset<br>(with<br>optional<br>threshold<br>voltage) | Internal<br>High-<br>Precise<br>Clock | reset<br>signal | Download<br>(to protect | RS485<br>Control | SO:<br>Price | Packa<br>SOP8<br>P16/DI<br>e of pacl<br>(RMB ¥ | P16<br>kages    |

|-----------------------------------------------|-----------------------------|-----------------|----------------|------------------|---|-----|--------|------------------------------------|-----------|-------------------------------------------|--------|------------|------------|-----|--------------------------------------------------------------------------------------|---------------------------------------|-----------------|-------------------------|------------------|--------------|------------------------------------------------|-----------------|

|                                               |                             |                 |                |                  |   |     | STC15V | V201S se                           | ries MCU  | Sel                                       | ec     | tion a     | nd Price T | abl |                                                                                      |                                       |                 |                         |                  |              |                                                |                 |

| STC15W201S                                    | 2.5-5.5                     | 1K              | 256            | 1 -              | 2 | -   | Y      | 5                                  | -         | Y                                         | 1      | 4K         | Y          | Y   | 16-level                                                                             | Y                                     | Y               | Y                       | Y                |              |                                                |                 |

| STC15W202S                                    | 2.5-5.5                     | 2K              | 256            | 1 -              | 2 | -   | Y      | 5                                  | -         | Y                                         | 1      | 3K         | Y          | Y   | 16-level                                                                             | Y                                     | Y               | Y                       | Y                |              |                                                |                 |

| STC15W203S                                    | 2.5-5.5                     | 3K              | 256            | 1 -              | 2 | -   | Y      | 5                                  | -         | Y                                         | 1      | 2K         | Y          | Y   | 8-level                                                                              | Y                                     | Y               | Y                       | Y                |              |                                                |                 |

| STC15W204S                                    | 2.5-5.5                     | 4K              | 256            | 1 -              | 2 | -   | Y      | 5                                  | -         | Y                                         | 1      | 1K         | Y          | Y   | 16-level                                                                             | Y                                     | Y               | Y                       | Y                |              |                                                |                 |

| IAP15W205S                                    | 2.5-5.5                     | 5K              | 256            | 1 -              | 2 | -   | Y      | 5                                  | -         | Y                                         | 1      | IAP        | Y          | Y   | 16-level                                                                             | Y                                     | Y               | Y                       | Y                | in u         | orogram<br>ser prog<br>an be u                 | gram<br>ised as |

| IRC15W207S<br>(Fixed internal<br>24MHz clock) | 2.5-5.5                     | 7.5K            | 256            | 1 -              | 2 | -   | Y      | 5                                  | -         | Y                                         | 1      | IAP        | Y          | Y   | Fixed                                                                                | Y                                     | Y               | N                       | N                | in u         | orogram<br>ser prog<br>an be u                 | gram<br>ised as |

Encryption Download: please burn source code with encryption key onto MCU in the factory. Then, you can make a simple update software just with one "update" button by fisrtly using the fuction "encrytion download" and then "release project" to update yourself code unabled to be intercepted when you need to upgrade your code.

To provide customized IC services

Because the last 7 bytes of the program area is stored mandatorily the contents of only global ID, the program space the user can actually use is 7 bytes smaller than the space shown in the selection table.

Conclusion: STC15W201S series MCU have: Two16-bit relaodable Timers/Counters that are Timer/Counter 0 and Timer/Counter 2; special power-down wake-up timer; 5 external interrupts INT0/INT1/INT2/INT3/INT4; a high-speed asynchronous serial port ---- UART; 1 Comparator; 1 data pointers ---- DPTR.

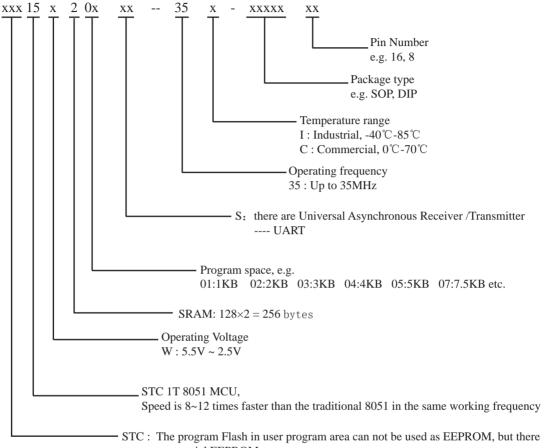

# 1.5 Naming rules of STC15W201S series MCU

are special EEPROM.

IAP: The program Flash in user program area can be used as EEPROM.

IRC: The program Flash in user program area can be used as EEPROM, and to regular use internal 24MHz clock

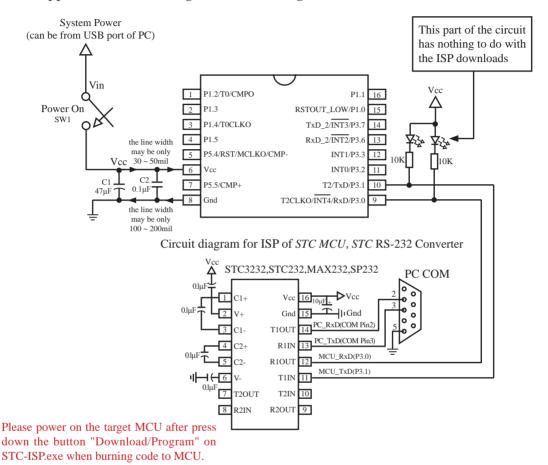

### 1.6 Application Circuit Diagram for ISP of STC15W201S series MCU

#### 1.6.1 Application Circuit Diagram for ISP using RS-232 Converter

Internal hghly reliable Reset, External reset circuit can be completely removed.

P5.4/RST/MCLKO pin factory defaults to the I/O port, which can be set as RST reset pin(active high) through the STC-ISP programmer.

Internal high-precise R/C clock( $\pm 3\%$ ),  $\pm 1\%$  temperature drift ( $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ ) while  $\pm 0.6\%$  in normal temperature ( $-20^{\circ}\text{C} \sim +65^{\circ}\text{C}$ ). External expensive crysal can be completely removed.

Recommend to add decoupling capacitor  $C1(47\mu F)$  and  $C2(0.1\mu F)$  between Vcc and Gnd that can remove power noise and improve the anti-interference ability.

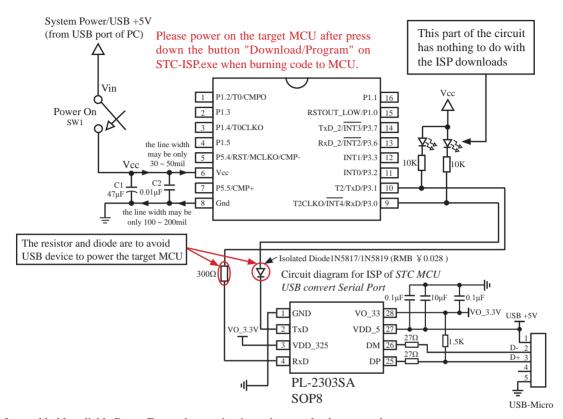

### 1.6.2 Application Circuit Diagram for ISP using USB Chip PL-2303SA to convert Serial Port

Internal hghly reliable Reset, External reset circuit can be completely removed.

P5.4/RST/MCLKO pin factory defaults to the I/O port, which can be set as RST reset pin(active high) through the STC-ISP programmer.

Internal high-precise R/C clock(  $\pm 3\%$  ),  $\pm 1\%$  temperature drift ( $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ ) while  $\pm 0.6\%$  in normal temperature ( $-20^{\circ}\text{C} \sim +65^{\circ}\text{C}$ ). External expensive crysal can be completely removed.

Recommend to add decoupling capacitor  $C1(47\mu F)$  and  $C2(0.1\mu F)$  between Vcc and Gnd that can remove power noise and improve the anti-interference ability.

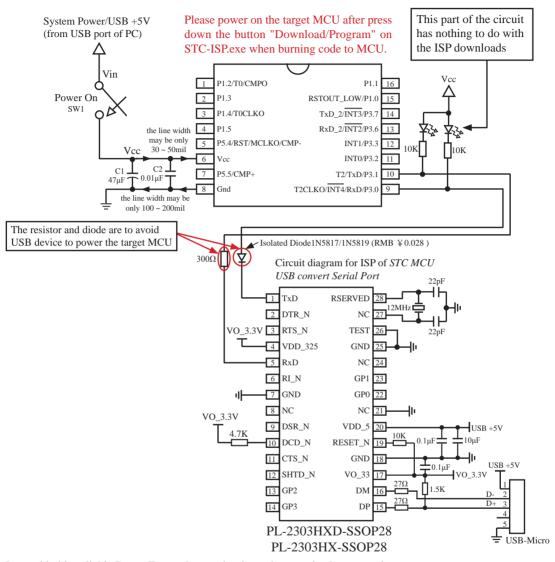

### 1.6.3 Application Circuit Diagram for ISP using USB Chip PL-2303HXD / PL-2303HX to convert Serial Port

Internal hghly reliable Reset, External reset circuit can be completely removed.

P5.4/RST/MCLKO pin factory defaults to the I/O port, which can be set as RST reset pin(active high) through the STC-ISP programmer.

Internal high-precise R/C clock( $\pm 3\%$ ),  $\pm 1\%$  temperature drift ( $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ ) while  $\pm 0.6\%$  in normal temperature ( $-20^{\circ}\text{C} \sim +65^{\circ}\text{C}$ ). External expensive crysal can be completely removed.

Recommend to add decoupling capacitor  $C1(47\mu F)$  and  $C2(0.1\mu F)$  between Vcc and Gnd that can remove power noise and improve the anti-interference ability.

# ${\bf 1.7~Pin~Descriptions~of~STC15W201S~series~MCU}$

| MNEMONIC    SOP  6    |                          | Din N | Jumbon |                |                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MNFMONIC                 | rm N  |        |                | DESCRIPTION                                                                                                                                                                 |

| P1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MINEMONIC                | SOP8  |        |                | DESCRIPTION                                                                                                                                                                 |

| PS.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |       | DII 10 | P1.0           | common I/O port PORT1[0]                                                                                                                                                    |

| P1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |       | 15     |                | 4 1 4 4 6 11 1 4 11 1 4                                                                                                                                                     |

| P1.2   Common I/O port PORT1[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RSTOUT_LOW               |       |        | RSTOUT_LOW     |                                                                                                                                                                             |

| P1.2/T0/CMPO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P1.1                     |       | 16     | common I/O por | rt PORT1[1]                                                                                                                                                                 |

| P1.3   2   common I/O port PORT1[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |       |        | P1.2           | common I/O port PORT1[2]                                                                                                                                                    |

| P1.3   2   common I/O port PORT1[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P1.2/T0/CMPO             |       | 1      | ТО             | External input of Timer/Counter 0                                                                                                                                           |

| P1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |       |        | CMPO           | The output port of reslut compared by comparator                                                                                                                            |

| P1.4/TOCLKO  P1.5  P3.0/RxD/INT4  P3.0/RxD/INT4  P3.0/RxD/INT4  P3.1/TxD/T2  P3.1/TxD/T2  P3.1/TxD/T2  P3.2/INT0  P3.3/INT1  P3.3/INT1  P3.6/INT2/RxD_2  P3.6/INT2/RxD_2  P3.7/INT3/TxD_2  P3.7/I | P1.3                     |       | 2      | common I/O por | rt PORT1[3]                                                                                                                                                                 |

| P1.5   4   common I/O port PORT1[5]   P3.0/RxD/INT4   5   9     P3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |       |        | P1.4           | common I/O port PORT1[5]                                                                                                                                                    |

| P3.0/RxD/INT4 /T2CLKO  P3.1/TxD/T2 6  P3.2/INT0 7  P3.3/INT1 8  P3.6/INT2/RxD_2  P3.6/INT2/RxD_2  P3.7/INT3/TxD_2  P3.7/INT3 very common I/O port PORT3[7]  External interrupt 0, which both can be generated on rising and falling edge. INT1 only can generate interrupt on falling edge if IT1 (TCON.2) is set to 1. And, INT1 both can generate interrupt on rising and falling edge. INT1 only can generate interrupt on rising and falling edge. INT2 supports power-down waking-up  RxD_2 Receive Data Port of UART  P3.7/INT3/TxD_2  P3.7/INT | P1.4/T0CLKO              |       | 3      | T0CLKO         | The pin can be configured for T0CLKO by setting INT_CLKO[0] bit                                                                                                             |

| P3.0/RxD/INT4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P1.5                     |       | 4      | common I/O po  | rt PORT1[5]                                                                                                                                                                 |

| P3.0/RxD/INT4 /T2CLKO  P3.1/TxD/T2  P3.1/TxD/T2  P3.1/TxD/T2  P3.2/INT0  P3.3/INT1  P3.3/INT1  P3.3/INT1  P3.3/INT1  P3.4/INT2/IxD_2  P3.6/INT2/RxD_2  P3.7/INT3/TxD_2  P3.7/INT3/TxD_2  P3.7/INT3/TxD_2  P3.6/INT3/TxD_2  P3.7/INT3/TxD_2  P3.7/INT |                          |       |        | P3.0           | common I/O port PORT3[0]                                                                                                                                                    |

| P3.0/RXD/INT4 /T2CLKO  9 INT4 INT4 supports power-down waking-up  T2 Clock Output The pin can be configured for T2CLKO by setting INT_CLKO[2] bit /T2CLKO  P3.1/TxD/T2 6 10 TxD Transit Data Port of UART  T2 External input of Timer/Counter 2  P3.2/INTO 7 11 External interrupt 0, which both can be generated on rising and falling edge. INT0 only can generate interrupt on rising and falling edge if ITO (TCON.0) is set to 0.  P3.3/INT1 8 12   P3.3   common I/O port PORT3[2]    External interrupt 0, which both can be generated on rising and falling edge if ITO (TCON.0) is set to 0.  1. And, INT0 both can generate interrupt on rising and falling edge if ITO (TCON.0) is set to 0.  P3.3/INT1   P3.3   common I/O port PORT3[3]    External interrupt 1, which both can be generated on rising and falling edge. INT1 only can generate interrupt on rising and falling edge if IT1 (TCON.2) is set to 1. And, INT1 both can generate interrupt on rising and falling edge if IT1 (TCON.2) is set to 0.  INT1 supports power-down waking-up  P3.6/INT2/RxD_2   P3.6   common I/O port PORT3[6]    External interrupt 2, which only can be generated on falling edge. INT2 supports power-down waking-up  P3.7/INT3/TxD_2   P3.7   common I/O port PORT3[7]    External interrupt 3, which only can be generated on falling edge. INT3 supports power-down waking-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |       |        | RxD            | Receive Data Port of UART                                                                                                                                                   |

| T2CLKO   T2CLKO   T2CLKO   T2CLKO   T2CLKO   T2CLKO   T2CLKO   T2CLKO   T3CLKO   T   | P3 0/RxD/INT4            |       |        | INITA          |                                                                                                                                                                             |

| T2CLKO The pin can be configured for T2CLKO by setting INT_CLKO[2] bit /T2CLKO  P3.1/TxD/T2 6 10 7xD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                        | 5     | 9      | 11114          | INT4 supports power-down waking-up                                                                                                                                          |

| P3.1/TxD/T2 6 10 Txn Transit Data Port of UART  T2 External input of Timer/Counter 2  P3.2 common I/O port PORT3[2]  External interrupt 0, which both can be generated on rising and falling edge. INTO only can generate interrupt on rising and falling edge if ITO (TCON.0) is set to 0.  P3.3/INT1 8 12 INT1   INT1   External interrupt 1, which both can be generated on rising and falling edge if ITO (TCON.0) is set to 0.  P3.3/INT1   INT1   External interrupt 1, which both can be generated on rising and falling edge. INT1 only can generate interrupt on falling edge if IT1 (TCON.2) is set to 1. And, INT1 both can generate interrupt on rising and falling edge if IT1 (TCON.2) is set to 0.  INT1 supports power-down waking-up  P3.6/INT2/RxD_2   P3.6   External interrupt 2, which only can be generated on falling edge. INT2 supports power-down waking-up  RxD_2   Receive Data Port of UART  P3.7   INT3   External interrupt 3, which only can be generated on falling edge. INT3 supports power-down waking-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |       |        | T2CLKO         | The pin can be configured for T2CLKO by setting INT_CLKO[2] bit                                                                                                             |

| P3.2/INT0 7 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |       |        | P3.1           | common I/O port PORT3[1]                                                                                                                                                    |

| P3.2/INTO  7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P3.1/TxD/T2              | 6     | 10     | TxD            | Transit Data Port of UART                                                                                                                                                   |

| P3.2/INT0 7 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |       |        | T2             | External input of Timer/Counter 2                                                                                                                                           |

| P3.2/INT0 7 11  INT0 only can generate interrupt on falling edge if IT0 (TCON.0) is set to 1. And, INT0 both can generate interrupt on rising and falling edge if IT0 (TCON.0) is set to 0.  P3.3 common I/O port PORT3[3]  External interrupt 1, which both can be generated on rising and falling edge. INT1 only can generate interrupt on falling edge if IT1 (TCON.2) is set to 1. And, INT1 both can generate interrupt on rising and falling edge if IT1 (TCON.2) is set to 0. INT1 supports power-down waking-up  P3.6/INT2/RxD_2 P3.6 common I/O port PORT3[6]  External interrupt 2, which only can be generated on falling edge. INT2 supports power-down waking-up  RxD_2 Receive Data Port of UART  P3.7/INT3/TxD_2 P3.7 common I/O port PORT3[7]  External interrupt 3, which only can be generated on falling edge. INT3 supports power-down waking-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |       |        | P3.2           | common I/O port PORT3[2]                                                                                                                                                    |

| P3.3/INT1  8  12  INT1  INT1  External interrupt 1, which both can be generated on rising and falling edge. INT1 only can generate interrupt on falling edge if IT1 (TCON.2) is set to 1. And, INT1 both can generate interrupt on rising and falling edge if IT1 (TCON.2) is set to 0. INT1 supports power-down waking-up  P3.6/INT2/RxD_2  P3.6  P3.6  External interrupt 2, which only can be generated on falling edge. INT2 supports power-down waking-up  RxD_2  Receive Data Port of UART  P3.7  External interrupt 3, which only can be generated on falling edge. INT3 supports power-down waking-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P3.2/INT0                | 7     | 11     | INT0           | INTO only can generate interrupt on falling edge if ITO (TCON.0) is set to 1. And, INTO both can generate interrupt on rising and falling edge if ITO                       |

| P3.3/INT1 8 12 INT1 only can generate interrupt on falling edge if IT1 (TCON.2) is set to 1. And, INT1 both can generate interrupt on rising and falling edge if IT1 (TCON.2) is set to 0. INT1 supports power-down waking-up  P3.6/INT2/RxD_2 P3.6 common I/O port PORT3[6]  External interrupt 2, which only can be generated on falling edge. INT2 supports power-down waking-up  RxD_2 Receive Data Port of UART  P3.7/INT3/TxD_2 P3.7 common I/O port PORT3[7]  External interrupt 3, which only can be generated on falling edge. INT3 supports power-down waking-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |       |        | P3.3           | common I/O port PORT3[3]                                                                                                                                                    |

| P3.6/INT2/RxD_2  13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P3.3/INT1                | 8     | 12     | INT1           | INT1 only can generate interrupt on falling edge if IT1 (TCON.2) is set to 1. And, INT1 both can generate interrupt on rising and falling edge if IT1 (TCON.2) is set to 0. |

| P3.6/INT2/RxD_2  INT2 INT2 supports power-down waking-up  RxD_2 Receive Data Port of UART  P3.7/INT3/TxD_2  P3.7/INT3/TxD_2  P3.7/INT3/TxD_2  P3.7/INT3 External interrupt 3, which only can be generated on falling edge.  INT3 supports power-down waking-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |       |        | P3.6           | common I/O port PORT3[6]                                                                                                                                                    |